L1, L2, L3, CCD y NUMA en CPUs Modernas

Caché Chiplets y Topologías Internas

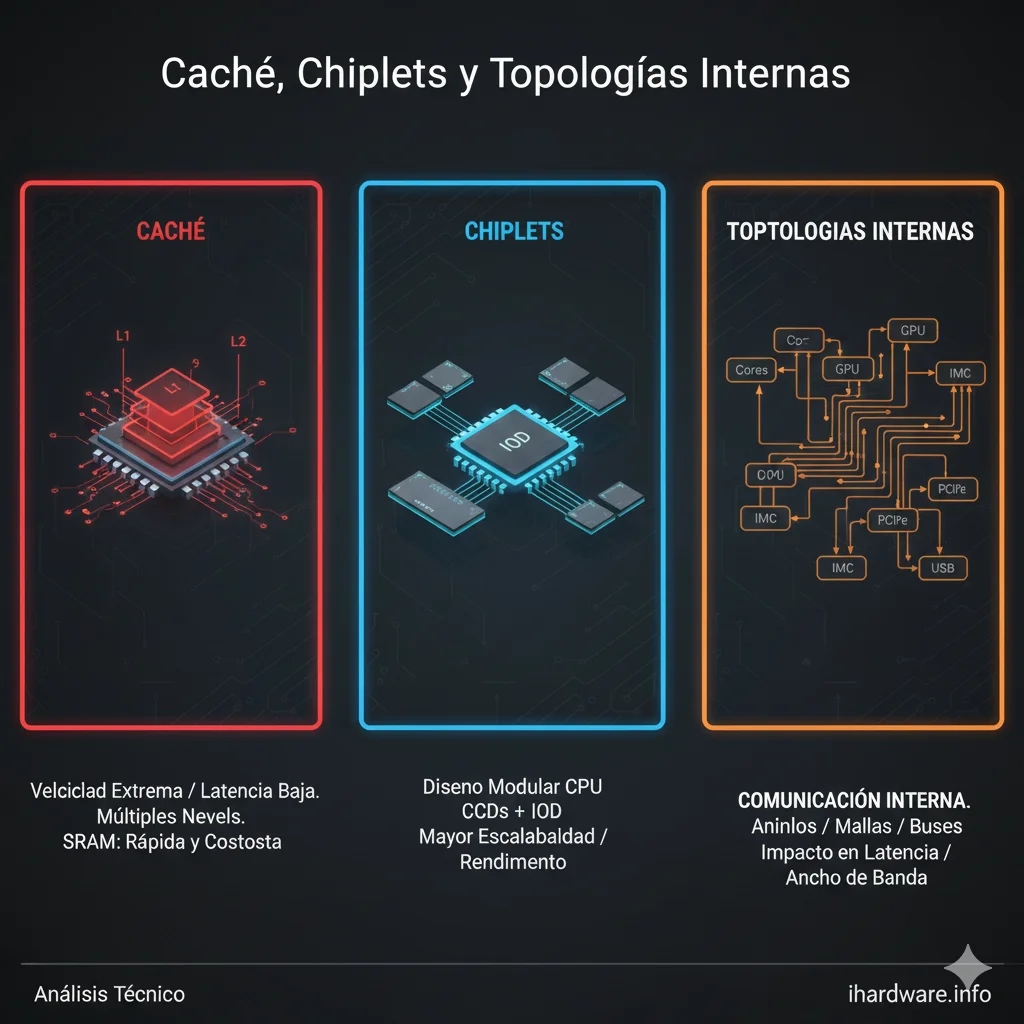

Caché Chiplets y Topologías Internas. La jerarquía de caché y la topología interna de un procesador determinan gran parte del rendimiento real, especialmente en cargas sensibles a latencia y en escenarios multi‑hilo. En arquitecturas modernas, conceptos como chiplets, CCD y NUMA introducen beneficios de escalabilidad, pero también nuevos cuellos de botella invisibles para el usuario.

Esta subcategoría explica cómo funcionan L1/L2/L3, cómo se organizan los núcleos en dominios de coherencia, y por qué la ubicación física de los datos importa tanto como la frecuencia o el IPC.

Jerarquía de caché: propósito y costes

La caché existe para ocultar la latencia de la memoria principal. Cada nivel sacrifica capacidad por menor latencia:

- L1: mínima latencia, capacidad muy limitada

- L2: equilibrio entre latencia y tamaño

- L3: compartida, mayor latencia, alta capacidad

Acceder a RAM es órdenes de magnitud más lento que acceder a L1.

Caché L1 y L2: proximidad y velocidad

L1

- Privada por núcleo

- Extremadamente rápida

- Altamente sensible a conflictos

L2

- Generalmente privada

- Más grande

- Latencia aún crítica

Un diseño eficiente minimiza fallos de L1/L2 para sostener IPC alto.

Caché L3: compartición y coherencia

La L3 actúa como amortiguador entre núcleos y memoria.

Aspectos clave:

- Compartida entre núcleos

- Latencia variable según topología

- Punto de contención frecuente

En cargas multi‑hilo, la L3 puede convertirse en el principal cuello de botella.

Protocolos de coherencia

Para mantener consistencia entre cachés se utilizan protocolos de coherencia.

Costes reales:

- Tráfico interno

- Invalidaciones frecuentes

- Latencias añadidas

Más núcleos implican mayor complejidad de coherencia.

Topologías internas

La forma en que los núcleos se conectan afecta directamente latencias.

Anillo

- Latencia predecible

- Escalabilidad limitada

Malla

- Mejor escalabilidad

- Latencias variables

Interconnect propietario

- Optimizado por fabricante

- Dependiente de frecuencia interna

Chiplets y CCD

Las arquitecturas por chiplets separan núcleos y otros bloques en múltiples dies.

Ventajas

- Mejor rendimiento por coste

- Escalabilidad

Costes

- Latencia inter‑chiplet

- Accesos remotos a caché

Los CCD definen dominios de latencia que afectan cargas sensibles.

NUMA: memoria no uniforme

En sistemas NUMA:

- No toda la memoria tiene la misma latencia

- La cercanía física importa

Problemas comunes:

- Hilos accediendo a memoria remota

- Caídas de rendimiento impredecibles

El sistema operativo y la afinidad de procesos son críticos.

Impacto en escenarios reales

Gaming

- Sensible a latencias L3

- Penalizado por accesos remotos

Render y compilación

- Mejor tolerancia a latencias

- Beneficio de caché grande

Virtualización

- NUMA crítico

- Afinidad mal configurada degrada rendimiento

Diagnóstico de problemas relacionados con caché

Síntomas frecuentes:

- Rendimiento inconsistente

- Escalado pobre con hilos

- Picos de latencia

La causa suele ser topología, no frecuencia.

Relación con otras subcategorías

Esta subcategoría conecta directamente con:

- Arquitectura de CPU

- IPC y latencias

- Núcleos e hilos

- IMC y memoria

- Comparativas CPU

Conclusión

El rendimiento moderno depende tanto de dónde están los datos como de cuántos ciclos ejecuta la CPU.

Comprender caché, chiplets y topologías internas permite:

- Interpretar benchmarks

- Diagnosticar cuellos de botella

- Optimizar afinidad y cargas

Esta subcategoría es clave para entender por qué CPUs similares se comportan de forma tan diferente en escenarios reales.