Arquitectura de CPU – Componentes Internos Funcionamiento y Diseño Moderno

Arquitectura de CPU – Componentes Internos Funcionamiento y Diseño Moderno. La arquitectura de un CPU es mucho más que el número de núcleos o la frecuencia anunciada. En procesadores modernos, el rendimiento, la eficiencia y la estabilidad dependen de cómo interactúan decenas de bloques internos, cada uno con funciones críticas y limitaciones físicas reales.

Este artículo está diseñado como referencia técnica intermedia–avanzada, profundizando en cada componente interno del CPU, su función, su impacto real en rendimiento y cómo se relacionan entre sí dentro de arquitecturas modernas (2025–2026).

1. El CPU como sistema completo

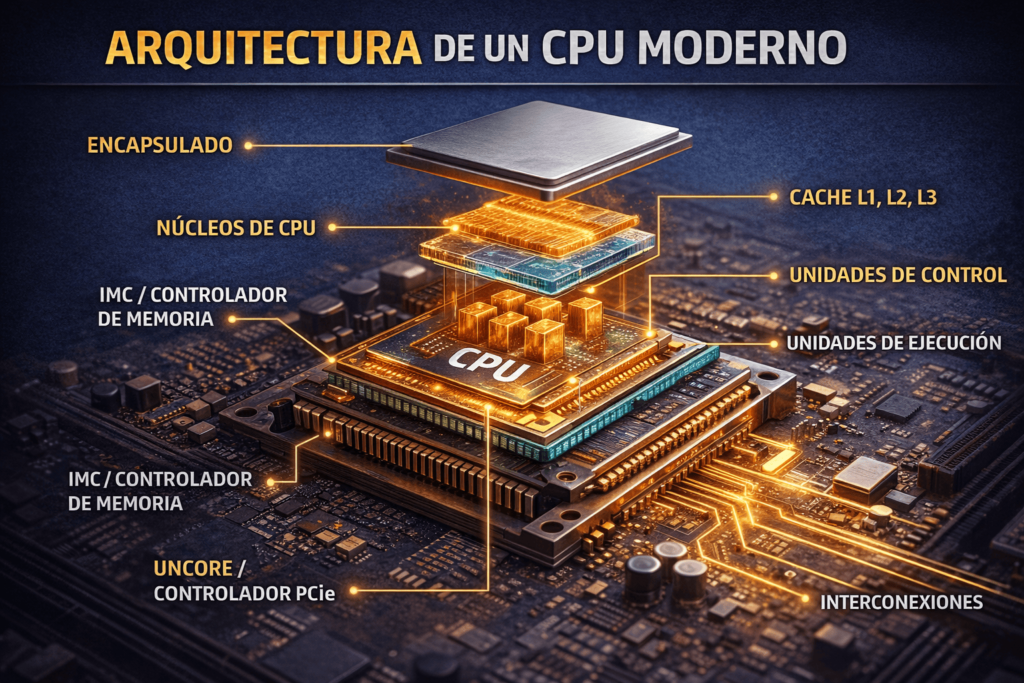

Un CPU moderno no es un bloque monolítico simple. Es un sistema altamente paralelo que integra:

- Front-end de instrucciones

- Back-end de ejecución

- Subsistemas de caché

- Interconexiones internas

- Controladores de memoria

- Lógica de energía y seguridad

Cada uno puede convertirse en factor limitante según la carga.

2. Front-End del CPU

2.1 Instruction Fetch

Responsable de:

- Obtener instrucciones desde la memoria o caché

- Predecir el flujo futuro del programa

Su eficiencia depende de:

- Ancho del fetch

- Precisión del predictor de saltos

Un front-end limitado estrecha el pipeline completo.

2.2 Branch Prediction (Predicción de saltos)

Los CPUs modernos ejecutan código antes de saber si es correcto. El predictor:

- Anticipa bifurcaciones

- Reduce burbujas en el pipeline

Errores de predicción:

- Vacían el pipeline

- Aumentan latencia efectiva

Arquitecturas modernas usan predictores híbridos y ML-like.

2.3 Decodificación de instrucciones

Convierte instrucciones complejas (x86) en micro-operaciones (µops).

Factores clave:

- Ancho de decodificación

- Caché de µops

Una decodificación limitada reduce IPC incluso con núcleos potentes.

3. Back-End del CPU

3.1 Scheduler y Reorder Buffer (ROB)

El ROB permite:

- Ejecución fuera de orden

- Reordenar resultados correctamente

Un ROB pequeño:

- Limita paralelismo

- Reduce IPC

3.2 Unidades de ejecución

ALU (Arithmetic Logic Unit)

- Operaciones enteras

- Críticas para código general

FPU (Floating Point Unit)

- Cálculos en coma flotante

- Clave en ciencia, render, simulación

SIMD / AVX / Vectoriales

- Operaciones masivas en paralelo

- Alto rendimiento pero alto consumo

Latencias y throughput definen rendimiento real.

3.3 Puertos de ejecución

Cada unidad se conecta a:

- Puertos internos

Congestión de puertos:

- Limita IPC

- Genera cuellos internos invisibles

4. Pipeline del CPU

El pipeline divide la ejecución en etapas:

- Fetch

- Decode

- Execute

- Writeback

Pipelines profundos:

- Altas frecuencias

- Penalización alta por errores

Pipelines cortos:

- Mejor latencia

- Menor frecuencia máxima

5. Subsistema de caché

5.1 Caché L1

- Muy rápida

- Tamaño limitado

- Latencia crítica

5.2 Caché L2

- Balance entre tamaño y latencia

- Impacta rendimiento sostenido

5.3 Caché L3

- Compartida

- Reduce accesos a RAM

- Clave en workloads multi-core

6. Interconexión interna

6.1 Anillos, mallas y fabric

Usados para:

- Comunicación entre núcleos

- Acceso a caché y memoria

Latencia de interconexión:

- Afecta escalado multi-core

- Impacta juegos y servidores

7. Controlador de Memoria (IMC)

Responsable de:

- Comunicación con RAM

- Manejo de latencias

Un IMC limitado:

- Reduce IPC efectivo

- Genera stuttering

8. Chiplets vs diseño monolítico

Monolítico

- Latencia baja

- Coste alto

Chiplets

- Escalabilidad

- Menor coste

- Mayor dependencia de interconexión

9. Energía, voltaje y gestión térmica

Bloques dedicados controlan:

- Boost

- Límites de potencia

- Protección térmica

El rendimiento real depende de frecuencia sostenida, no pico.

10. Seguridad y mitigaciones

Incluye:

- Mitigaciones Spectre/Meltdown

- Impacto real en rendimiento

Arquitectura moderna busca minimizar penalizaciones.

11. Relación arquitectura vs rendimiento real

No existe un solo factor dominante:

- IPC

- Frecuencia

- Latencia

- Eficiencia

Todo depende del equilibrio del diseño.

Entender la arquitectura interna del CPU permite:

- Diagnosticar problemas reales

- Elegir hardware correctamente

- Evitar marketing engañoso

Un CPU moderno es un sistema complejo donde cada bloque importa.